16-laach PCBs jouwe de kompleksiteit en fleksibiliteit nedich troch moderne elektroanyske apparaten. Skilled ûntwerp en seleksje fan steapele sekwinsjes en interlayer ferbining metoaden binne kritysk foar it berikken fan optimale board prestaasjes. Yn dit artikel sille wy oerwagings, rjochtlinen en bêste praktiken ûndersykje om ûntwerpers en yngenieurs te helpen effisjinte en betroubere 16-laach circuit boards te meitsjen.

1.Understanding de basis fan 16 laach PCBs Stacking Sequence

1.1 Definysje en doel fan stacking folchoarder

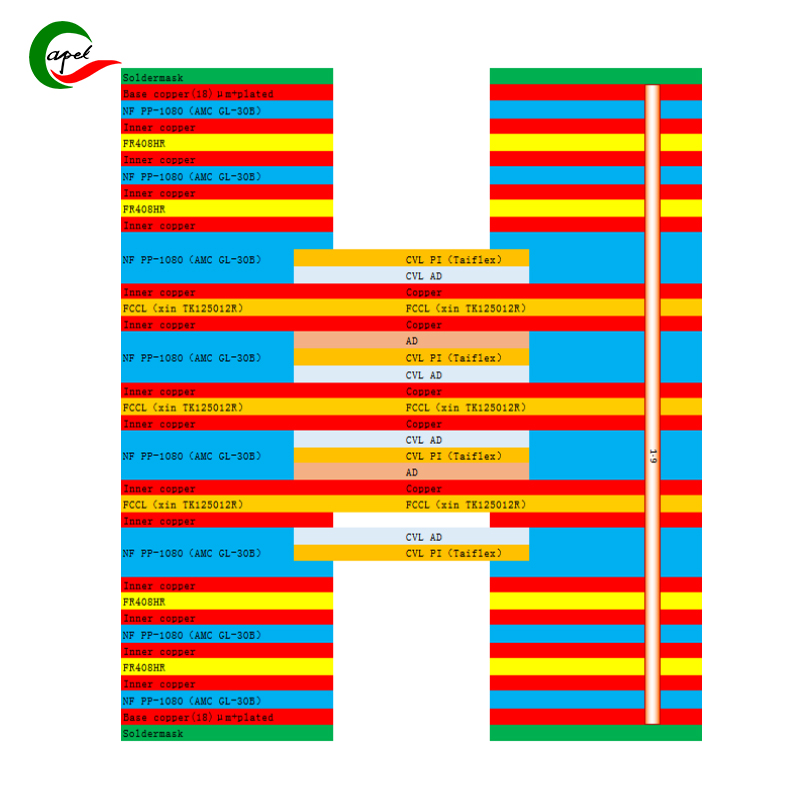

Stacking folchoarder ferwiist nei de regeling en folchoarder wêryn materialen lykas koper en isolearjende lagen wurde laminearre tegearre te foarmjen in multi-laach circuit board. de steapel.

It haaddoel fan 'e stapelingssekwinsje is om de fereaske elektryske en meganyske eigenskippen fan it bestjoer te berikken. It spilet in fitale rol by it bepalen fan de impedânsje fan in circuit board, sinjaalyntegriteit, machtferdieling, thermysk behear, en fabrikaazjemooglikheid. De steapele folchoarder hat ek ynfloed op de algemiene prestaasjes, betrouberens en manufacturability fan it bestjoer.

1.2 Faktoaren dy't ynfloed hawwe op it ûntwerp fan stapelsekwinsje: D'r binne ferskate faktoaren dy't moatte wurde beskôge by it ûntwerpen fan de stapelsekwinsje fan in

16-laach PCB:

a) Elektryske oerwegingen:De yndieling fan sinjaal-, macht- en grûnfleantugen moatte wurde optimalisearre om goede sinjaalintegriteit, impedânsjekontrôle en reduksje fan elektromagnetyske ynterferinsje te garandearjen.

b) Termyske oerwegingen:De pleatsing fan krêft- en grûnfleantugen en it opnimmen fan thermyske fias helpe om waarmte effektyf te dissipearjen en de optimale wurktemperatuer fan 'e komponint te behâlden.

c) Produksjebeperkingen:De keazen stapelingssekwinsje moat rekken hâlde mei de mooglikheden en beheiningen fan it PCB-produksjeproses, lykas materiaalbeskikberens, oantal lagen, drill aspect ratio,en alignment accuracy.

d) Kostenoptimalisaasje:De seleksje fan materialen, oantal lagen en opstapelkompleksiteit moatte konsistint wêze mei it projektbudzjet, wylst de fereaske prestaasjes en betrouberens garandearje.

1.3 Algemiene soarten stapelsekwinsjes fan 16-laach circuitboard: D'r binne ferskate gewoane stapelsekwinsjes foar 16-laach

PCB, ôfhinklik fan de winske prestaasjes en easken. Guon mienskiplike foarbylden omfetsje:

a) Symmetryske stapelfolchoarder:Dizze folchoarder omfettet it pleatsen fan sinjaallagen symmetrysk tusken macht- en grûnlagen om goede sinjaalyntegriteit, minimale crosstalk en lykwichtige waarmtedissipaasje te berikken.

b) Opfolgjende stapelingssekwinsje:Yn dizze folchoarder, de sinjaal lagen binne sequentially tusken de macht en grûn lagen. It soarget foar gruttere kontrôle oer laacharrangement en is foardielich foar it foldwaan oan spesifike easken foar sinjaalintegriteit.

c) Mingde stapelopdracht:Dit omfettet in kombinaasje fan symmetryske en opfolgjende stapelopdrachten. It lit maatwurk en optimalisearjen fan de opmaak foar spesifike dielen fan it bestjoer.

d) Sinjaalgefoelige stapelsekwinsje:Dizze sekwinsje pleatst gefoelige sinjaallagen tichter by it grûnflak foar bettere lûdimmuniteit en isolemint.

2.Key oerwagings foar seleksje fan 16-laach PCB-stapelsekwinsje:

2.1 Overwegingen foar sinjaalintegriteit en machtintegriteit:

De stapeling folchoarder hat in wichtige ynfloed op de sinjaal yntegriteit en macht yntegriteit fan it bestjoer. De juste pleatsing fan sinjaal- en macht / grûnfleantugen is kritysk om it risiko fan sinjaalferfoarming, lûd en elektromagnetyske ynterferinsje te minimalisearjen. Wichtige oerwagings omfetsje:

a) Pleatsing fan sinjaallaach:High-speed sinjaal lagen moatte wurde pleatst tichtby de grûn fleantúch te foarsjen in lege-inductance werom paad en minimalisearje lûd coupling. Sinjaallagen moatte ek soarchfâldich oanlein wurde om sinjaalskew en lingte-oerienkomst te minimalisearjen.

b) Power plane distribúsje:De stapelingssekwinsje moat soargje foar adekwate distribúsje fan machtfleantúch om machtyntegriteit te stypjen. Genôch krêft- en grûnfleantugen moatte strategysk pleatst wurde om spanningsfallen, impedânsje-diskontinuïteiten en lûdskeppeling te minimalisearjen.

c) Ontkoppelkondensatoren:Goede pleatsing fan ûntkoppelingskondensatoren is kritysk om te soargjen foar adekwate macht oerdracht en minimalisearje macht oanbod lûd. De steapele folchoarder moat soargje foar tichtby en tichtby de decoupling capacitors oan de macht en grûn fleantugen.

2.2 Termyske behear en waarmte dissipaasje:

Effisjint termyske behear is kritysk foar it garandearjen fan betrouberens en prestaasjes fan circuit board. De stapelingssekwinsje moat rekken hâlde mei de juste pleatsing fan krêft- en grûnfleantugen, thermyske fias en oare koelmeganismen. Wichtige oerwagings omfetsje:

a) Power plane distribúsje:Adekwate ferdieling fan macht en grûn fleantugen troch de steapel helpt direkte waarmte fuort fan gefoelige komponinten en soarget foar unifoarme temperatuer ferdieling oer it bestjoer.

b) Termyske fias:De stapeling folchoarder moat soargje foar effektive termyske fia pleatsing te fasilitearjen waarmte dissipation fan de binnenste laach nei de bûtenste laach of waarmte sink. Dit helpt om lokale hot spots te foarkommen en soarget foar effisjinte waarmtedissipaasje.

c) Komponint pleatsing:Stacking folchoarder moat beskôgje de regeling en de buert fan ferwaarming komponinten te kommen oververhitting. Goede ôfstimming fan komponinten mei koelmeganismen lykas heatsinks of fans moatte ek wurde beskôge.

2.3 Produksjebeheiningen en kostenoptimalisaasje:

De stapelingssekwinsje moat rekken hâlde mei produksjebeheiningen en kostenoptimalisaasje, om't se in wichtige rol spylje yn 'e helberens en betelberens fan it bestjoer. Beskôgings omfetsje:

a) Materiaal beskikberens:De selektearre stapelingssekwinsje moat oerienkomme mei de beskikberens fan materialen en har kompatibiliteit mei it selekteare PCB-produksjeproses.

b) Oantal lagen en kompleksiteit:De stapelingssekwinsje moat wurde ûntworpen binnen de beheiningen fan it selekteare PCB-produksjeproses, rekken hâldend mei faktoaren lykas oantal lagen, drill-aspektferhâlding en ôfstimmingsnauwkeurigens.

c) Kostenoptimalisaasje:De stapelingssekwinsje moat it gebrûk fan materialen optimalisearje en de kompleksiteit fan produksje ferminderje sûnder de fereaske prestaasjes en betrouberens te kompromittearjen. It moat as doel hawwe om kosten te minimalisearjen ferbûn mei materiaalôffal, proseskompleksiteit en montage.

2.4 Laach ôfstimming en sinjaal oerspraak:

De stapelingssekwinsje moat problemen mei laachôfstimming oanpakke en sinjaal oerspraak minimalisearje dy't de sinjaalyntegriteit negatyf kin beynfloedzje. Wichtige oerwagings omfetsje:

a) Symmetrysk stapeljen:Symmetrysk steapele fan sinjaallagen tusken macht- en grûnlagen helpt om keppeling te minimalisearjen en crosstalk te ferminderjen.

b) Differinsjaal pear routing:De stapelingssekwinsje moat tastean dat de sinjaallagen goed ôfstimd wurde foar effisjinte routing fan differinsjaalsignalen mei hege snelheid. Dit helpt om sinjaalyntegriteit te behâlden en crosstalk te minimalisearjen.

c) Sinjaal skieding:De stapelingssekwinsje moat de skieding fan gefoelige analoge en digitale sinjalen beskôgje om crosstalk en ynterferinsje te ferminderjen.

2.5 Impedânsjekontrôle en RF / mikrogolfyntegraasje:

Foar RF / mikrogolfapplikaasjes is de stapelingssekwinsje kritysk om juste impedânsjekontrôle en yntegraasje te berikken. Wichtige oerwagings omfetsje:

a) Regele impedânsje:De stapelingssekwinsje moat regele impedânsjeûntwerp mooglik meitsje, rekken hâldend mei faktoaren lykas spoarbreedte, dielektrike dikte en laacharrangement. Dit soarget foar juste sinjaalpropagaasje en impedânsje-oerienkomst foar RF- / mikrogolfsignalen.

b) Pleatsing fan sinjaallaach:RF / magnetron sinjalen moatte wurde strategysk pleatst tichtby de bûtenste laach te minimalisearje ynterferinsje fan oare sinjalen en soargje foar bettere sinjaal fuortplanting.

c) RF-ôfskerming:De stapeling folchoarder moat befetsje goede pleatsing fan grûn en shielding lagen te isolearjen en beskermjen RF / magnetron sinjalen út ynterferinsje.

3.Interlayer Connection Methods

3.1 Trochgatten, bline gatten en begroeven gatten:

Vias wurde in soad brûkt yn printe circuit board (PCB) design as in middel fan ferbinen ferskillende lagen. Se wurde boarre gatten troch alle lagen fan de PCB en wurde plated te foarsjen elektryske kontinuïteit. Troch gatten jouwe in sterke elektryske ferbining en binne relatyf maklik te meitsjen en te reparearjen. Lykwols, se fereaskje gruttere drill bit maten, dy't nimme up weardefolle romte op de PCB en beheine routing opsjes.

Blinen en begroeven fias binne alternative metoaden foar ferbining tusken lagen dy't foardielen biede yn romtegebrûk en routingfleksibiliteit.

Blinde fias wurde boarre út de PCB oerflak en terminate yn binnenste lagen sûnder trochjaan troch alle lagen. Se tastean ferbinings tusken neistlizzende lagen wylst it litten fan djippere lagen ûnoantaaste. Dit soarget foar effisjinter gebrûk fan boerdromte en ferleget it oantal boorgaten. Begroeven fias, oan 'e oare kant, binne gatten dy't folslein ynsletten binne yn' e binnenste lagen fan 'e PCB en net útwreidzje nei de bûtenste lagen. Se jouwe ferbinings tusken binnenste lagen sûnder ynfloed op de bûtenste lagen. Begraven fias hawwe grutter romte-besparjende foardielen as troch-gatten en bline fias omdat se net nimme gjin romte yn de bûtenste laach.

De kar fan trochgatten, bline fias en begroeven fias hinget ôf fan 'e spesifike easken fan it PCB-ûntwerp. Trochgatten wurde typysk brûkt yn ienfâldiger ûntwerpen as wêr't robústiteit en reparaasje primêr soargen binne. Yn ûntwerpen mei hege tichtheid wêr't romte in krityske faktor is, lykas handheld apparaten, smartphones en laptops, wurde bline en begroeven fias de foarkar.

3.2 Micropore enHDI technology:

Microvias binne gatten mei lytse diameter (meastentiids minder as 150 mikron) dy't hege tichtheid interlayer ferbinings yn PCBs leverje. Se biede wichtige foardielen yn miniaturisaasje, sinjaalintegriteit en routingfleksibiliteit.

Microvias kinne wurde ferdield yn twa soarten: troch-hole microvias en bline microvias. Microvias wurde konstruearre troch it boarjen fan gatten út it boppeste oerflak fan 'e PCB en útwreidzje troch alle lagen. Blinde mikrovia's, lykas de namme al fermoeden docht, útwreidzje allinich nei spesifike ynterne lagen en penetrearje net alle lagen.

High-density interconnect (HDI) is in technology dy't mikrovias en avansearre produksjetechniken brûkt om hegere circuittichtens en prestaasjes te berikken. HDI-technology soarget foar it pleatsen fan lytsere komponinten en strakkere routing, wat resulteart yn lytsere foarmfaktoaren en hegere sinjaalintegriteit. HDI-technology biedt ferskate foardielen boppe tradisjonele PCB-technology yn termen fan miniaturisaasje, ferbettere sinjaalpropagaasje, fermindere sinjaalferfoarming en ferbettere funksjonaliteit. It makket multilayer-ûntwerpen mooglik mei meardere mikrovia's, wêrtroch ynterkonneksjelingten ferkoarte wurde en parasitêre kapasitânsje en induktânsje ferminderje.

HDI-technology makket ek it gebrûk fan avansearre materialen mooglik, lykas hege frekwinsje laminaten en tinne dielektrike lagen, dy't kritysk binne foar RF / mikrofoaveapplikaasjes. It soarget foar bettere impedânsjekontrôle, ferminderet sinjaalferlies en soarget foar betroubere sinjaaltransmission mei hege snelheid.

3.3 Interlayer ferbining materialen en prosessen:

De seleksje fan interlayer ferbining materialen en techniken is kritysk foar it garandearjen fan goede elektryske prestaasjes, meganyske betrouberens en manufacturability fan PCBs. Guon meast brûkte materialen en techniken foar interlayerferbining binne:

a) Koper:Koper wurdt in soad brûkt yn conductive lagen en fias fan PCB's fanwege syn treflike conductivity en solderability. It wurdt normaal pleatst op it gat om in betroubere elektryske ferbining te leverjen.

b) Soldering:Soldertechniken, lykas welle-solderen of reflow-soldering, wurde faak brûkt om elektryske ferbiningen te meitsjen tusken trochgeande gatten op PCB's en oare komponinten. Tapasse solderpasta oan 'e fia en tapasse waarmte om it soldeer te smelten en in betroubere ferbining te foarmjen.

c) Elektroplating:Electroplating techniken lykas electroless koper plating of electrolytic koper wurde brûkt om platen fias te ferbetterjen conductivity en soargje foar goede elektryske ferbinings.

d) Ferbining:Biningtechniken, lykas adhesive bonding of thermocompression bonding, wurde brûkt om laachstruktueren byinoar te ferbinen en betroubere ynterferbiningen te meitsjen.

e) Dielektrysk materiaal:De kar fan dielektrysk materiaal foar de PCB-stapel is kritysk foar interlayer-ferbiningen. Laminaten mei hege frekwinsje lykas FR-4 of Rogers-laminaten wurde faak brûkt om goede sinjaalintegriteit te garandearjen en sinjaalferlies te minimalisearjen.

3.4 Trochsneedûntwerp en betsjutting:

It dwerstrochsneed ûntwerp fan 'e PCB-stapel bepaalt de elektryske en meganyske eigenskippen fan' e ferbiningen tusken lagen. Wichtige oerwagings foar dwerstrochsneedûntwerp omfetsje:

a) Laacharrangement:De regeling fan sinjaal-, macht- en grûnfleantugen binnen in PCB-stapel beynfloedet sinjaalyntegriteit, machtyntegriteit en elektromagnetyske ynterferinsje (EMI). Goede pleatsing en ôfstimming fan sinjaal lagen mei macht en grûn fleantugen helpt minimalisearje lûd coupling en soargje lege inductance werom paden.

b) Impedânsje kontrôle:Dwars-seksje-ûntwerp moat rekken hâlde mei regele impedânsjeeasken, foaral foar hege snelheid digitale as RF / mikrogolfsignalen. Dit omfettet passende seleksje fan dielektrike materialen en dikten om de winske karakteristike impedânsje te berikken.

c) Termyske behear:De trochsneed ûntwerp moat beskôgje effektive waarmte dissipation en termyske behear. Juste pleatsing fan macht en grûn fleantugen, termyske fias, en komponinten mei cooling meganismen (lykas heatsinks) helpe dissipate waarmte en behâlden optimale wurking temperatueren.

d) Mechanyske betrouberens:Seksje-ûntwerp moat meganyske betrouberens beskôgje, benammen yn tapassingen dy't kinne wurde ûnderwurpen oan termyske fytsen of meganyske stress. Goede seleksje fan materialen, bondingstechniken en stapelkonfiguraasje helpe de strukturele yntegriteit en duorsumens fan 'e PCB te garandearjen.

4.Design Rjochtlinen foar 16-Layer PCB

4.1 Laach tawizing en distribúsje:

By it ûntwerpen fan in 16-laach circuit board is it wichtich om de lagen foarsichtich te allocearjen en te fersprieden om prestaasjes en sinjaalyntegriteit te optimalisearjen. Hjir binne guon rjochtlinen foar tier tawizing

en distribúsje:

Bepale it oantal fereaske sinjaallagen:

Beskôgje de kompleksiteit fan it circuit ûntwerp en it oantal sinjalen dat moatte wurde omlaat. Allokearje genôch sinjaallagen om alle fereaske sinjalen te foldwaan, soargje foar adekwate routingromte en foarkom oermjittichoerlêst. Tawize grûn- en krêftfleantugen:

Tawize op syn minst twa ynderlike lagen oan grûn en macht fleantugen. In grûn fleantúch helpt te bieden in stabile referinsje foar sinjalen en minimalisearje elektromagnetyske ynterferinsje (EMI). It macht fleantúch jout in lege-impedânsje macht distribúsje netwurk dat helpt te minimalisearje spanning drippen.

Skieden gefoelige sinjaallagen:

Ofhinklik fan 'e applikaasje kin it nedich wêze om gefoelige of hege snelheid sinjaallagen te skieden fan lawaaierige of hege krêftige lagen om ynterferinsje en oerspraak te foarkommen. Dit kin dien wurde troch it pleatsen fan tawijd grûn- of krêftfleantugen tusken har of troch isolaasjelagen te brûken.

Sinjaallagen gelijkmatig fersprieden:

Fersprieden sinjaallagen lykmjittich troch de boardstapel om keppeling tusken neistlizzende sinjalen te minimalisearjen en sinjaalyntegriteit te behâlden. Foarkom it pleatsen fan sinjaallagen njonken elkoar yn itselde stapelgebiet om interlayer-oerspraak te minimalisearjen.

Tink oan hege frekwinsje sinjalen:

As jo ûntwerp sinjalen mei hege frekwinsje befettet, beskôgje dan om de hege frekwinsje-sinjaallagen tichter by de bûtenste lagen te pleatsen om effekten fan transmisjeline te minimalisearjen en fertraging foar fuortplanting te ferminderjen.

4.2 Routing en sinjaalrûte:

Routing en sinjaaltrace-ûntwerp binne kritysk om goede sinjaalintegriteit te garandearjen en ynterferinsje te minimalisearjen. Hjir binne wat rjochtlinen foar yndieling en sinjaalrouting op 16-laach circuit boards:

Brûk bredere spoaren foar sinjalen mei hege stroom:

Foar sinjalen dy't hege stroom drage, lykas krêft- en grûnferbiningen, brûke bredere spoaren om ferset en spanningsfal te minimalisearjen.

Oerienkommende impedânsje foar sinjalen mei hege snelheid:

Foar sinjalen mei hege snelheid, soargje derfoar dat de spoarimpedânsje oerienkomt mei de karakteristike impedânsje fan 'e oerdrachtline om refleksjes en sinjaaldemping te foarkommen. Brûk kontrolearre impedansûntwerptechniken en korrekte berekkeningen fan spoarbreedte.

Minimalisearje spoarlingten en crossoverpunten:

Hâld trace lingten sa koart mooglik en ferminderje it oantal crossover punten te ferminderjen parasitêr capacitance, inductance, en ynterferinsje. Optimalisearje de pleatsing fan komponinten en brûk spesjale routinglagen om lange, komplekse spoaren te foarkommen.

Separate hege snelheid en lege snelheid sinjalen:

Separearje hege- en lege-snelheid sinjalen om de ynfloed fan lûd op hege-snelheid sinjalen te minimalisearjen. Plak sinjalen mei hege snelheid op tawijde sinjaallagen en hâld se fuort fan komponinten mei hege krêft of lûd.

Brûk differinsjaalpearen foar sinjalen mei hege snelheid:

Om lûd te minimalisearjen en sinjaalyntegriteit te behâlden foar differinsjaalsignalen mei hege snelheid, brûk differinsjaalpaar-routingtechniken. Hâld de impedânsje en lingte fan differinsjaalpearen oerienkomme om sinjaalskew en crosstalk te foarkommen.

4.3 Grûnlaach en macht laach distribúsje:

Goede ferdieling fan grûn- en krêftfleantugen is kritysk foar it berikken fan goede krêftyntegriteit en it ferminderjen fan elektromagnetyske ynterferinsje. Hjir binne wat rjochtlinen foar opdrachten foar grûn- en krêftfleantúch op 16-laach circuit boards:

Tawize tawijd grûn- en krêftfleantugen:

Tawize op syn minst twa ynderlike lagen foar tawijd grûn en macht fleantugen. Dit helpt om grûnlussen te minimalisearjen, EMI te ferminderjen en in weromreispaad mei lege impedânsje te leverjen foar sinjalen mei hege frekwinsje.

Skieden digitale en analoge grûnfleantugen:

As it ûntwerp digitale en analoge seksjes hat, is it oan te rieden om aparte grûnfleantugen foar elke seksje te hawwen. Dit helpt om lûdskeppeling tusken de digitale en analoge seksjes te minimalisearjen en ferbetteret sinjaalintegriteit.

Plak grûn- en krêftfleantugen tichtby sinjaalfleantugen:

Plak grûn- en krêftfleantugen tichtby de sinjaalfleantugen dy't se fiede om loopgebiet te minimalisearjen en lûdopfang te ferminderjen.

Brûk meardere fias foar macht fleantugen:

Brûk meardere fias om macht fleantugen te ferbinen om de macht evenredich te fersprieden en de impedânsje fan machtplan te ferminderjen. Dit helpt te minimalisearjen oanbod spanning drippen en ferbetteret macht yntegriteit.

Foarkom smelle hals yn macht fleantugen:

Foarkom smelle nekken yn macht fleantugen as se kinne feroarsaakje hjoeddeistige crowding en fergrutsje wjerstân, resultearret yn spanning drippen en macht fleanmasine inefficiencies. Brûk sterke ferbiningen tusken ferskate krêftflakgebieten.

4.4 Termyske pad en fia pleatsing:

Goede pleatsing fan termyske pads en fias is kritysk foar it effektyf dissipearjen fan waarmte en it foarkommen fan komponinten fan oververhitting. Hjir binne wat rjochtlinen foar termyske pad en fia pleatsing op 16-laach circuit boards:

Plak termyske pad ûnder waarmte-generearjende komponinten:

Identifisearje de waarmte-generearjende komponint (lykas in krêftfersterker of IC mei hege krêft) en pleats it thermyske pad direkt derûnder. Dizze termyske pads jouwe in direkte termyske paad om waarmte oer te bringen nei de ynterne termyske laach.

Brûk meardere thermyske fias foar waarmte dissipaasje:

Brûk meardere thermyske fias om de thermyske laach en de bûtenste laach te ferbinen om effisjinte waarmtedissipaasje te leverjen. Dizze fias kinne wurde pleatst yn in staggered patroan om de termyske pad te berikken sels waarmte ferdieling.

Beskôgje thermyske impedânsje en laachstapeling:

By it ûntwerpen fan termyske fias, beskôgje de termyske impedânsje fan it bestjoer materiaal en laach stackup.Optimize fia grutte en spacing te minimalisearje termyske ferset en maksimalisearje waarmte dissipation.

4.5 Pleatsing fan komponinten en sinjaalintegriteit:

Goede pleatsing fan komponinten is kritysk foar it behâld fan sinjaalintegriteit en it minimalisearjen fan ynterferinsje. Hjir binne wat rjochtlinen foar it pleatsen fan komponinten op in 16-laach circuit board:

Groep relatearre komponinten:

Groep relatearre komponinten dy't diel útmeitsje fan itselde subsysteem of hawwe sterke elektryske ynteraksjes. Dit ferminderet spoarlingte en minimearret sinjaaldemping.

Hâld hege snelheid komponinten tichtby:

Pleats komponinten mei hege snelheid, lykas oscillators mei hege frekwinsje of mikrocontrollers, tichtby elkoar om spoarlingten te minimalisearjen en goede sinjaalintegriteit te garandearjen.

Minimalisearje de spoarlingte fan krityske sinjalen:

Minimalisearje de spoarlingte fan krityske sinjalen om fertraging fan fuortplanting en sinjaaldemping te ferminderjen. Plak dizze komponinten sa ticht mooglik.

Separate gefoelige komponinten:

Skeakelje lûdgefoelige komponinten, lykas analoge komponinten of sensoren op leech nivo, fan komponinten mei hege krêft as lawaaierige komponinten om ynterferinsje te minimalisearjen en sinjaalintegriteit te behâlden.

Tink oan ûntkoppelingskondensatoren:

Plak ûntkoppelingskondensatoren sa ticht mooglik by de krêftpinnen fan elke komponint om skjinne krêft te leverjen en spanningsfluktuaasjes te minimalisearjen. Dizze kondensatoren helpe de stroomfoarsjenning te stabilisearjen en lûdkeppeling te ferminderjen.

5.Simulaasje en analyse ark foar Stack-Up Design

5.1 Software foar 3D-modellering en simulaasje:

3D-modellerings- en simulaasjesoftware is in wichtich ark foar stackup-ûntwerp, om't it ûntwerpers mooglik makket firtuele foarstellings fan PCB-stackups te meitsjen. De software kin lagen, komponinten en har fysike ynteraksjes visualisearje. Troch de stapeling te simulearjen kinne ûntwerpers potinsjele problemen identifisearje lykas sinjaal oerspraak, EMI, en meganyske beheiningen. It helpt ek om de regeling fan komponinten te ferifiearjen en it algemiene PCB-ûntwerp te optimalisearjen.

5.2 Tools foar analyze fan sinjaalintegriteit:

Tools foar analyse fan sinjaalintegriteit binne kritysk foar it analysearjen en optimalisearjen fan de elektryske prestaasjes fan PCB-stapels. Dizze ark brûke wiskundige algoritmen om sinjaalgedrach te simulearjen en te analysearjen, ynklusyf impedânsjekontrôle, sinjaalrefleksjes en lûdskeppeling. Troch simulaasje en analyze út te fieren, kinne ûntwerpers potinsjele problemen mei sinjaalintegriteit identifisearje betiid yn it ûntwerpproses en de nedige oanpassingen meitsje om betroubere sinjaaltransmission te garandearjen.

5.3 Tools foar termyske analyze:

Thermal analyze ark spylje in wichtige rol yn stackup design troch analysearjen en optimalisearjen fan termyske behear fan PCBs. Dizze ark simulearje waarmtedissipaasje en temperatuerferdieling binnen elke laach fan 'e stapel. Troch sekuer modellering fan macht dissipaasje en waarmte oerdracht paden, ûntwerpers kinne identifisearje hot spots, optimalisearjen fan de pleatsing fan koper lagen en termyske fias, en soargje foar goede koeling fan krityske komponinten.

5.4 Untwerp foar fabrikaazje:

Untwerp foar manufacturability is in wichtich aspekt fan stackup design. D'r binne in ferskaat oan software-ark beskikber dy't kinne helpe te soargjen dat de selekteare stack-up effisjint kin wurde produsearre. Dizze ark jouwe feedback oer de helberens fan it berikken fan de winske stapeling, rekken hâldend mei faktoaren lykas materiaalbeskikberens, laachdikte, fabrikaazjeproses en fabrikaazjekosten. Se helpe ûntwerpers ynformeare besluten te nimmen om stapeljen te optimalisearjen om de fabrikaazje te ferienfâldigjen, it risiko fan fertragingen te ferminderjen en de opbringsten te ferheegjen.

6.Step-by-Step Design Process foar 16-laach PCBs

6.1 Samling fan earste easken:

Yn dizze stap sammelje alle nedige easken foar 16-laach PCB-ûntwerp. Begryp de funksjonaliteit fan 'e PCB, fereaske elektryske prestaasjes, meganyske beheiningen, en elke spesifike ûntwerprjochtlinen as noarmen dy't moatte wurde folge.

6.2 Tawizing en regeling fan komponinten:

Neffens easken, allocearje komponinten op 'e PCB en bepale har arranzjemint. Beskôgje faktoaren lykas sinjaalyntegriteit, termyske oerwagings, en meganyske beheiningen. Groepearje komponinten basearre op elektryske skaaimerken en pleats se strategysk op it boerd om ynterferinsje te minimalisearjen en sinjaalstream te optimalisearjen.

6.3 Stapelûntwerp en laachferdieling:

Bepale it stack-up ûntwerp foar de 16-laach PCB. Tink oan faktoaren lykas dielektrike konstante, termyske konduktiviteit en kosten om it passende materiaal te selektearjen. Tawize sinjaal, macht, en grûn fleantugen neffens elektryske easken. Pleats grûn- en krêftfleantugen symmetrysk om in lykwichtige stapel te garandearjen en sinjaalyntegriteit te ferbetterjen.

6.4 Sinjaalrouting en routingoptimalisaasje:

Yn dizze stap wurde sinjaalspoaren trochstjoerd tusken komponinten om goede impedânsjekontrôle, sinjaalintegriteit te garandearjen en sinjaal oerspraak te minimalisearjen. Optimalisearje routing om de lingte fan krityske sinjalen te minimalisearjen, foar te kommen dat gefoelige spoaren oerstekke, en skieding behâlde tusken sinjalen mei hege snelheid en lege snelheid. Brûk differinsjaal-pearen en kontrolearre impedânsje-routingtechniken as it nedich is.

6.5 Interlayer ferbiningen en fia pleatsing:

Plan de pleatsing fan ferbinende fias tusken lagen. Bepale de passende fia type, lykas troch gat of blyn gat, basearre op laach oergongen en komponint ferbinings. Optimalisearje fia yndieling om sinjaalrefleksjes, impedânsje-diskontinuïteiten te minimalisearjen en sels ferdieling op 'e PCB te behâlden.

6.6 Finale ûntwerpferifikaasje en simulaasje:

Foarôfgeand oan fabrikaazje wurde definitive ûntwerpferifikaasje en simulaasjes útfierd. Brûk simulaasje-ark om PCB-ûntwerpen te analysearjen foar sinjaalyntegriteit, krêftyntegriteit, thermysk gedrach en fabrikaazje. Ferifiearje it ûntwerp tsjin inisjele easken en meitsje de nedige oanpassingen om prestaasjes te optimalisearjen en produsearberens te garandearjen.

Gearwurkjen en kommunisearje mei oare belanghawwenden lykas elektryske yngenieurs, meganyske yngenieurs, en produksjeteams yn it heule ûntwerpproses om te soargjen dat alle easken foldien wurde en potinsjele problemen wurde oplost. Kontrolearje en iterearje regelmjittich ûntwerpen om feedback en ferbetteringen op te nimmen.

7.Industry Best Practices and Case Studies

7.1 Súksesfolle gefallen fan 16-laach PCB-ûntwerp:

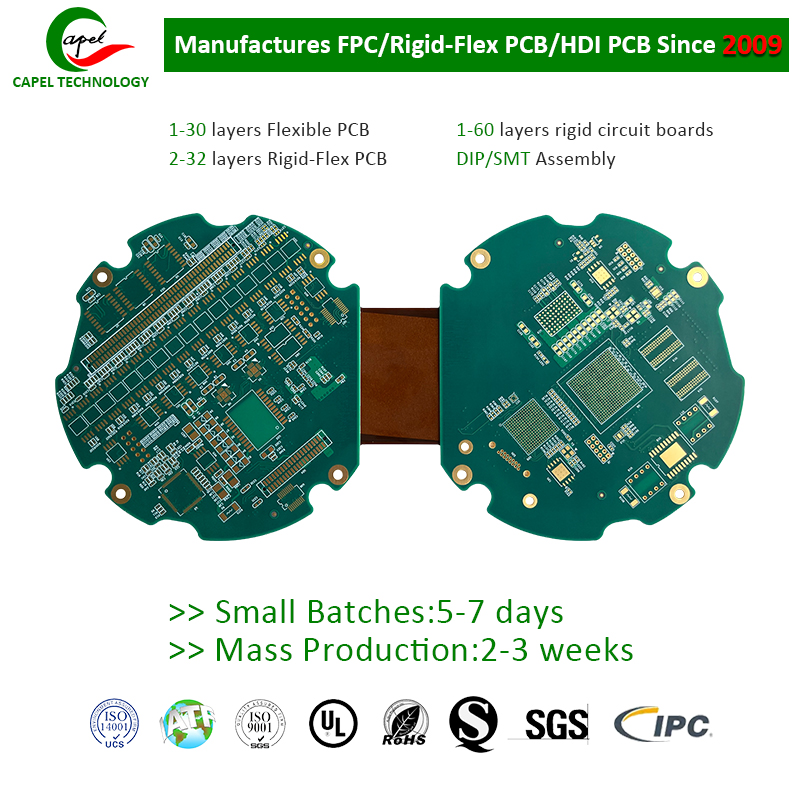

Case study 1:Shenzhen Capel Technology Co., Ltd. mei súkses ûntwurpen in 16-laach PCB foar hege-snelheid netwurk apparatuer. Troch soarchfâldich te beskôgjen fan sinjaalintegriteit en krêftferdieling, berikke se superieure prestaasjes en minimalisearje elektromagnetyske ynterferinsje. De kaai foar har sukses is in folslein optimalisearre stack-up-ûntwerp mei gebrûk fan kontroleare impedânsje-routingtechnology.

Case Study 2:Shenzhen Capel Technology Co., Ltd. ûntwurp in 16-laach PCB foar in kompleks medysk apparaat. Troch it brûken fan in kombinaasje fan oerflak mount en troch-hole komponinten, se berikke in kompakt mar machtich ûntwerp. Soartige komponint pleatsing en effisjinte routing soargje foar treflike sinjaal yntegriteit en betrouberens.

7.2 Learje fan mislearrings en foarkomme falkûlen:

Case Study 1:Guon pcb-fabrikanten tsjinkamen problemen mei sinjaalintegriteit yn it 16-laach PCB-ûntwerp fan kommunikaasjeapparatuer. De redenen foar mislearring wiene ûnfoldwaande beskôging fan impedânsjekontrôle en gebrek oan goede ferdieling fan grûnflak. De learde les is om de easken foar sinjaalintegriteit soarchfâldich te analysearjen en strikte ûntwerprjochtlinen foar impedânsjekontrôle te hanthavenjen.

Case Study 2:Guon pcb-makkers stiene produksjeútdagings mei syn 16-laach PCB fanwegen ûntwerpkompleksiteit. De oerbrûk fan bline fias en ticht ynpakt komponinten liedt ta produksje en assemblage swierrichheden. De learde les is om in lykwicht te meitsjen tusken ûntwerpkompleksiteit en manufacturability sjoen de mooglikheden fan 'e keazen PCB-fabrikant.

Om falkûlen en falkûlen te foarkommen yn 16-laach PCB-ûntwerp, is it krúsjaal om:

a.Grutte begripe de easken en beheinings fan it ûntwerp.

b.Stacked konfiguraasjes dy't optimalisearje sinjaal yntegriteit en macht distribúsje. c.Carefully fersprieden en regelje komponinten te optimalisearjen prestaasjes en ferienfâldigjen manufacturing.

d. Soargje foar goede rûtetechniken, lykas it kontrolearjen fan impedânsje en it foarkommen fan oermjittich gebrûk fan bline fias.

e.Gearwurkjen en kommunisearje effektyf mei alle belanghawwenden belutsen by it ûntwerp proses, ynklusyf elektryske en meganyske yngenieurs en manufacturing teams.

f.Perform wiidweidich ûntwerp ferifikaasje en simulaasje te identifisearjen en korrizjearje potinsjele problemen foardat manufacturing.

Post tiid: Sep-26-2023

Rêch